Introduction

IC Design & Verification Tools are essential software platforms that allow engineers to design, simulate, and validate integrated circuits (ICs) before they go into manufacturing. These tools automate and streamline the complex process of circuit design, logic verification, timing analysis, and physical layout, reducing errors and accelerating development cycles. For modern semiconductor projects—ranging from microprocessors and AI accelerators to analog-mixed signal chips—these tools ensure that circuits function as intended, comply with design rules, and meet performance goals.

In today’s high-speed, high-density IC market, design complexity has skyrocketed, and verification bottlenecks can dramatically delay time-to-market. Advanced IC design tools now incorporate AI-assisted verification, automated formal checks, multi-domain simulation, cloud collaboration, and scalable HPC compute, helping teams optimize performance while reducing risk.

Common Use Cases

- ASIC and SoC design for consumer electronics and computing

- FPGA design and verification for industrial and telecommunications applications

- Analog and mixed-signal IC development

- Memory design and verification

- Design-for-test (DFT) and manufacturing sign-off

What Buyers Should Evaluate

- RTL design, synthesis, and optimization capabilities

- Logic verification (simulation, formal, emulation)

- Timing, power, and signal integrity analysis

- Analog/mixed-signal support

- Physical layout and DRC/LVS checking

- Multi-domain simulation and co-verification

- Automation, scripting, and AI-assisted workflows

- Integration with manufacturing and fabrication flows

- Scalability for HPC and cloud environments

- Licensing flexibility and cost efficiency

Best for: Semiconductor engineers, R&D IC teams, FPGA designers, verification engineers, and enterprises developing cutting-edge chips.

Not ideal for: Hobbyists, occasional prototypers, or teams only doing simple digital logic testing; lighter FPGA or schematic-only tools may suffice.

Key Trends in IC Design & Verification Tools

- AI-assisted synthesis and verification accelerate RTL-to-gate workflows

- Cloud-enabled simulation and emulation for distributed IC teams

- Full-chip formal verification becoming standard for complex SoCs

- Analog and mixed-signal co-simulation to reduce design iteration cycles

- High-level synthesis (HLS) for algorithm-to-hardware design

- Integration with manufacturing and DFM flows for production-ready designs

- Automated testbench generation and reusable verification IP

- Open-source and community-based frameworks supplement commercial tools

- HPC and GPU acceleration for faster verification and simulation

- Subscription and usage-based licensing to scale with project needs

How We Selected These Tools (Methodology)

- Evaluated industry adoption and mindshare across ASIC, FPGA, and analog teams

- Assessed completeness of design and verification features

- Considered solver, simulation, and emulation performance

- Reviewed security and deployment flexibility

- Checked integration with existing EDA ecosystem

- Evaluated automation, AI, and productivity-enhancing features

- Balanced enterprise vs SMB vs research-focused tools

- Considered community and support infrastructure

- Checked scalability for cloud/HPC workflows

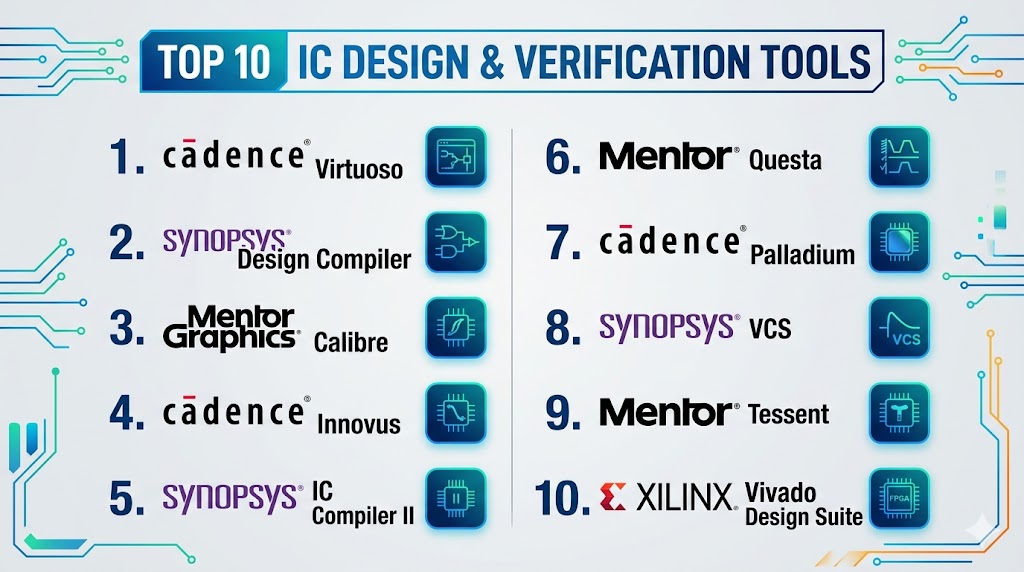

Top 10 IC Design & Verification Tools

#1 — Cadence Virtuoso

Short description: Enterprise-standard platform for analog, mixed-signal, and RF IC design with full verification capabilities.

Key Features

- Analog and mixed-signal circuit design

- Layout, routing, and DRC/LVS verification

- Multi-domain simulation (thermal, analog, RF)

- Integration with design libraries and IP

- AI-assisted verification workflows

- Manufacturing sign-off and DFM checks

Pros

- Extremely reliable for complex ICs

- Integrated analog-mixed signal capabilities

- Broad industry adoption

Cons

- Expensive for smaller teams

- High learning curve

Platforms / Deployment

Windows / Linux / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- SPICE simulators and IP libraries

- Foundry PDKs and verification suites

- Scripting and automation APIs

Support & Community

Strong enterprise support, training, and active user community.

#2 — Synopsys Design Compiler

Short description: Leading RTL synthesis and optimization platform for digital ASIC and SoC design.

Key Features

- RTL synthesis and gate-level optimization

- Multi-clock and multi-domain support

- Timing and power analysis

- Technology-aware optimizations

- Integration with verification flows

- Formal and simulation support

Pros

- Industry-standard for high-performance digital ICs

- Scalable for large SoC projects

Cons

- Enterprise pricing

- Limited analog/mixed-signal support

Platforms / Deployment

Linux / Windows / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- RTL simulators

- Verification and emulation tools

- Foundry PDKs

Support & Community

Enterprise support with extensive documentation.

#3 — Mentor Graphics Calibre

Short description: Gold-standard tool for physical verification and DRC/LVS checks in advanced node IC design.

Key Features

- Layout versus schematic (LVS) checking

- Design rule checking (DRC)

- Mask data preparation

- Yield and DFM analysis

- Multi-layer verification

- Advanced reporting

Pros

- Critical for production-ready ICs

- Supports leading-edge process nodes

Cons

- Complex interface

- High licensing costs

Platforms / Deployment

Linux / Windows / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- CAD design flows

- Foundry rule decks

- Manufacturing sign-off systems

Support & Community

Strong vendor support and industry-wide adoption.

#4 — Cadence Innovus

Short description: Digital place-and-route and full-chip implementation tool optimized for high-performance SoCs.

Key Features

- Automated floorplanning and placement

- Timing closure and optimization

- Power, clock, and signal integrity management

- Integration with synthesis and verification flows

- Multi-corner, multi-mode analysis

- AI-assisted optimization

Pros

- High performance for complex SoCs

- Tight integration with Cadence ecosystem

Cons

- Requires expert users

- Enterprise-focused licensing

Platforms / Deployment

Linux / Windows / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- RTL synthesis tools

- Verification and Calibre tools

- Foundry PDK integration

Support & Community

Vendor enterprise support with extensive documentation.

#5 — Synopsys IC Compiler II

Short description: Place-and-route tool for digital ICs and SoCs with advanced optimization and verification capabilities.

Key Features

- Global and detail routing

- Timing, power, and signal integrity optimization

- Multi-corner, multi-mode design

- Hierarchical design support

- Integration with verification and synthesis flows

Pros

- Enterprise-grade scalability

- Handles large SoCs efficiently

Cons

- Expensive and complex

- Requires dedicated training

Platforms / Deployment

Linux / Windows / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Synopsys synthesis and verification tools

- Foundry PDKs

- Simulation flows

Support & Community

Commercial support and training resources.

#6 — Mentor Questa

Short description: Verification platform offering simulation, formal verification, and coverage analysis for ASIC/FPGA design.

Key Features

- RTL simulation and debug

- UVM-based verification

- Formal verification and property checking

- Code coverage and assertion support

- Integration with synthesis and emulation flows

Pros

- Comprehensive verification suite

- Supports large-scale SoC projects

Cons

- High learning curve

- Costly for smaller teams

Platforms / Deployment

Linux / Windows / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Synthesis tools

- Emulators and FPGA flows

- Verification IP libraries

Support & Community

Professional support and extensive documentation.

#7 — Cadence Palladium

Short description: Hardware emulation platform for SoC verification, enabling rapid bug detection and system validation.

Key Features

- Full-chip hardware emulation

- Integration with RTL simulation and verification

- Multi-language support (SystemVerilog, VHDL)

- High-speed regression testing

- Debugging and coverage analysis

Pros

- Significantly reduces verification cycles

- Handles very large designs

Cons

- Very expensive

- Requires specialized hardware

Platforms / Deployment

Linux / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Simulation tools

- Verification IP

- Scripting APIs

Support & Community

Enterprise-grade support and training.

#8 — Synopsys VCS

Short description: High-performance RTL simulation platform for digital IC verification.

Key Features

- RTL simulation and debug

- Multi-language support

- Coverage-driven verification

- UVM and assertion-based methodologies

- Scalable parallel simulation

Pros

- Fast and reliable simulation

- Widely used in enterprise SoC verification

Cons

- Enterprise pricing

- Requires verification expertise

Platforms / Deployment

Linux / Windows / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Synthesis and emulation tools

- Verification IP

- Debug and coverage tools

Support & Community

Enterprise support with extensive user community.

#9 — Mentor Tessent

Short description: DFT (Design for Test) and silicon test platform for IC validation and manufacturing readiness.

Key Features

- Scan insertion and ATPG

- Fault simulation and coverage

- DFT verification

- Silicon test planning

- Integration with synthesis and verification flows

Pros

- Critical for manufacturing yield and test

- Supports complex SoC designs

Cons

- Specialized skill set required

- Enterprise-level pricing

Platforms / Deployment

Linux / Windows / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Synthesis and verification tools

- Manufacturing test flows

- Debug and analysis suites

Support & Community

Commercial vendor support and training resources.

#10 — Xilinx Vivado Design Suite

Short description: FPGA design and verification platform with synthesis, simulation, and implementation tools.

Key Features

- RTL synthesis and implementation

- Timing analysis and optimization

- Simulation and debug

- IP core management

- Hardware-in-the-loop support

Pros

- Optimized for Xilinx FPGAs

- Integration with hardware test benches

Cons

- FPGA-specific

- Limited ASIC support

Platforms / Deployment

Windows / Linux / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Xilinx IP cores

- Hardware validation boards

- Simulation workflows

Support & Community

Strong vendor support and active FPGA community.

Comparison Table

| Tool Name | Best For | Platform(s) | Deployment | Standout Feature | Public Rating |

|---|---|---|---|---|---|

| Cadence Virtuoso | Analog/Mixed-Signal IC | Win/Linux | Hybrid | Multi-domain IC design | N/A |

| Synopsys Design Compiler | Digital ASIC/SoC | Win/Linux | Hybrid | RTL synthesis | N/A |

| Mentor Calibre | Physical Verification | Win/Linux | Hybrid | DRC/LVS checks | N/A |

| Cadence Innovus | Digital SoC | Win/Linux | Hybrid | Place & route | N/A |

| Synopsys IC Compiler II | SoC Implementation | Win/Linux | Hybrid | Optimization & routing | N/A |

| Mentor Questa | Verification Suite | Win/Linux | Hybrid | Simulation + formal | N/A |

| Cadence Palladium | Hardware Emulation | Linux | Hybrid | Full-chip emulation | N/A |

| Synopsys VCS | RTL Simulation | Win/Linux | Hybrid | Fast simulation | N/A |

| Mentor Tessent | DFT & Silicon Test | Win/Linux | Hybrid | Manufacturing test | N/A |

| Xilinx Vivado | FPGA Design | Win/Linux | Hybrid | FPGA synthesis & simulation | N/A |

Evaluation & Scoring of IC Design & Verification Tools

| Tool | Core | Ease | Integrations | Security | Performance | Support | Value | Weighted Total |

|---|---|---|---|---|---|---|---|---|

| Cadence Virtuoso | 10 | 6 | 9 | 6 | 10 | 9 | 6 | 8.15 |

| Synopsys Design Compiler | 10 | 6 | 8 | 6 | 10 | 8 | 6 | 7.95 |

| Mentor Calibre | 9 | 5 | 8 | 6 | 9 | 8 | 6 | 7.7 |

| Cadence Innovus | 9 | 6 | 8 | 6 | 9 | 8 | 6 | 7.8 |

| Synopsys IC Compiler II | 9 | 5 | 8 | 6 | 9 | 8 | 6 | 7.7 |

| Mentor Questa | 9 | 6 | 8 | 6 | 9 | 8 | 6 | 7.8 |

| Cadence Palladium | 9 | 5 | 7 | 6 | 9 | 7 | 6 | 7.6 |

| Synopsys VCS | 9 | 6 | 8 | 6 | 9 | 8 | 6 | 7.8 |

| Mentor Tessent | 8 | 6 | 7 | 6 | 8 | 8 | 6 | 7.3 |

| Xilinx Vivado | 8 | 7 | 7 | 6 | 8 | 7 | 6 | 7.35 |

Scores are comparative. Higher totals indicate broader overall fit across enterprise and mid-market IC teams, but specific project needs may favor specialized tools.

Which IC Design & Verification Tool Is Right for You?

Solo / Freelancer

- Vivado → FPGA-focused small team projects

- KiCad or lightweight FPGA design tools → hobby or prototype projects

SMB

- Questa or Innovus → mid-size digital/analog teams

- PADS/Calibre lite → PCB-centric IC modules

Mid-Market

- Synopsys IC Compiler II → SoC design optimization

- Innovus + Questa → RTL + verification combo

Enterprise

- Cadence Virtuoso → Analog/mixed-signal ICs

- Synopsys Design Compiler → ASIC and SoC

Budget vs Premium

- Budget: Vivado, PADS-lite, open-source FPGA tools

- Premium: Virtuoso, Innovus, IC Compiler II

Feature Depth vs Ease of Use

- Depth: Virtuoso, IC Compiler II, Calibre

- Ease: Vivado, Questa

Integrations & Scalability

- Enterprise: Virtuoso, Innovus, Palladium

- Mid-market: Questa, IC Compiler II

Security & Compliance Needs

- Cloud deployments require governance; most enterprise tools do not publicly disclose SOC/ISO compliance.

Frequently Asked Questions (FAQs)

1. What is an IC design & verification tool?

Software that allows engineers to design and validate integrated circuits before manufacturing.

2. Which tool is easiest for FPGA design?

Xilinx Vivado offers an accessible FPGA-focused workflow.

3. Do these tools support analog design?

Virtuoso, Innovus, and Questa support analog and mixed-signal workflows.

4. Are IC design tools expensive?

Enterprise-grade ASIC/SoC tools are costly; small teams may use FPGA or open-source alternatives.

5. Can these tools simulate circuits?

Yes—simulation, formal verification, and emulation are core features.

6. What is formal verification?

Mathematical analysis to prove design correctness without exhaustive simulation.

7. Do these tools help with manufacturing?

Yes—Calibre and Tessent provide DRC/LVS checks and test planning.

8. Can teams collaborate on IC projects?

Many tools offer multi-user, cloud-enabled, or version-controlled workflows.

9. Is there an open-source option?

Vivado WebPACK and FPGA-lite tools exist; most enterprise ASIC tools are proprietary.

10. Should I prioritize depth or ease of use?

Complex ASIC/SoC teams prioritize depth; FPGA or prototyping teams prioritize usability.

Conclusion

IC Design & Verification Tools are the backbone of modern semiconductor innovation. Enterprise platforms like Cadence Virtuoso and Synopsys Design Compiler deliver unmatched depth for analog, digital, and mixed-signal designs, while FPGA-focused tools like Vivado serve prototyping and smaller-scale teams. Verification-heavy workflows benefit from Mentor Questa and Cadence Palladium, and DFT specialists rely on Tessent and Calibre. The best tool depends on your team size, IC complexity, and project goals. Shortlist 2–3 tools, test real RTL/SoC workflows, and validate verification, synthesis, and manufacturing integration before committing for maximum productivity.

Find Trusted Cardiac Hospitals

Compare heart hospitals by city and services — all in one place.

Explore Hospitals