Introduction

IC Design & Verification Tools are specialized software solutions used to design, simulate, and validate integrated circuits (ICs) before they are manufactured. These tools streamline complex semiconductor design processes, ensuring functionality, performance, and manufacturability of ICs. In 2026 and beyond, with increasing chip complexity and AI-driven design workflows, these tools are critical for reducing time-to-market and mitigating costly design errors.

Real-world use cases include verifying signal integrity in high-speed chips, simulating power and thermal behavior in processors, detecting logical and functional design errors, optimizing analog and digital circuits, and ensuring compliance with semiconductor fabrication standards. Buyers should evaluate features such as simulation accuracy, automation capabilities, integration with existing EDA workflows, support for advanced verification methodologies, ease of use, scalability, security, and cost-effectiveness.

Best for: semiconductor engineers, IC design teams, hardware startups, and large semiconductor firms needing advanced verification, simulation, and design automation.

Not ideal for: small projects or hobbyist designs where manual design or basic open-source tools suffice.

Key Trends in IC Design & Verification Tools

- AI-assisted synthesis and optimization are increasingly integrated into IC design workflows.

- Cloud-based simulation and verification offer scalable compute resources and collaboration.

- Early-stage verification using formal methods reduces costly late-stage errors.

- Multi-die and 3D IC designs drive adoption of advanced verification techniques.

- Integration with system-level simulation tools enables faster co-design of software and hardware.

- Low-power and high-efficiency design focus increases demand for power analysis capabilities.

- Interoperability with standard EDA toolchains ensures smoother handoff between teams.

- Automated regression testing reduces repetitive verification workloads.

- Enhanced debugging tools and visualizations simplify error identification and root cause analysis.

- Flexible licensing models support both startups and large enterprises.

How We Selected These Tools (Methodology)

- Evaluated market adoption and mindshare among semiconductor design teams.

- Assessed feature completeness across digital, analog, and mixed-signal verification.

- Considered performance and reliability signals from user reports and benchmarks.

- Reviewed security posture for collaborative cloud-based design and IP protection.

- Examined integrations with popular EDA suites and verification ecosystems.

- Evaluated suitability across different company sizes and project scales.

- Prioritized tools offering advanced AI/automation features.

- Considered documentation, onboarding, and user community support.

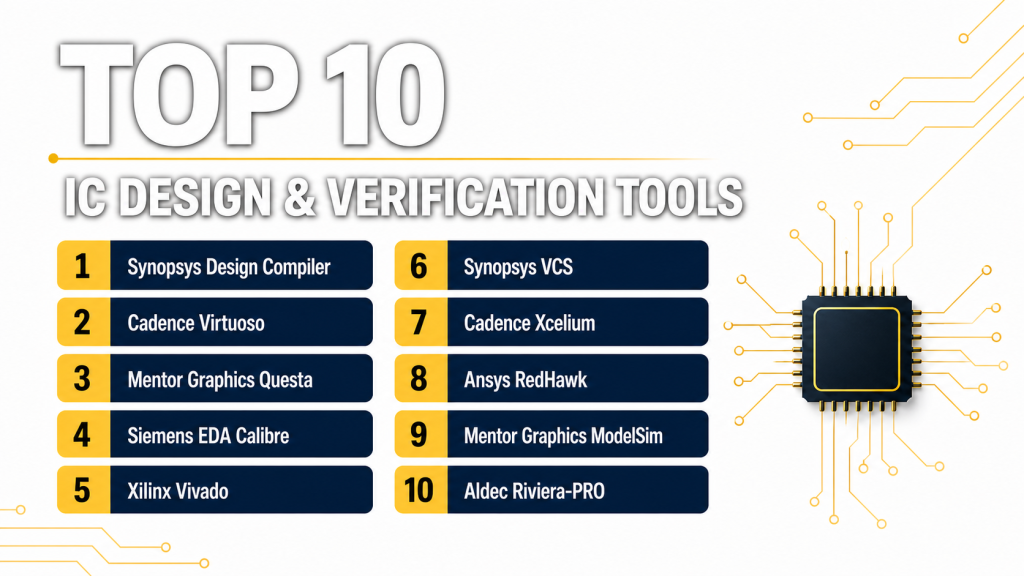

Top 10 IC Design & Verification Tools

1 — Synopsys Design Compiler

Short description: A leading RTL synthesis tool used by semiconductor companies for high-performance IC design, offering AI-assisted optimization for digital logic synthesis.

Key Features

- RTL synthesis with timing optimization

- AI-driven design space exploration

- Low-power design support

- Integration with verification flows

- Multi-corner, multi-mode analysis

Pros

- Proven enterprise adoption

- High-quality synthesis results

- Scales for large IC designs

Cons

- Complex learning curve

- Licensing can be costly

- Limited support for analog circuits

Platforms / Deployment

- Linux, Windows

- Cloud / On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Integrates seamlessly with Synopsys verification tools and third-party EDA suites.

- Verilog, VHDL, SystemVerilog support

- DFT and scan chain integration

- AI optimization APIs

- Timing analysis tools

Support & Community

- Comprehensive documentation, enterprise support tiers, active user community

2 — Cadence Virtuoso

Short description: Cadence Virtuoso is a premier platform for analog, RF, and mixed-signal IC design, providing simulation and layout capabilities for complex semiconductor circuits.

Key Features

- Analog/mixed-signal simulation

- Layout automation and verification

- Spectre and ADE integration

- Parasitic extraction and modeling

- Signal integrity analysis

Pros

- High accuracy for analog/mixed-signal

- Robust simulation engines

- Strong support for advanced IC processes

Cons

- Expensive licensing

- Steep learning curve

- Limited digital-only capabilities

Platforms / Deployment

- Linux, Windows

- Cloud / On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Cadence Virtuoso integrates with Cadence’s PCB and verification toolchains.

- SPICE simulation support

- DRC/LVS verification

- Third-party modeling libraries

- APIs for custom scripts

Support & Community

- Enterprise-level support and dedicated training programs, active community forums

3 — Mentor Graphics Questa

Short description: Questa is a verification platform for functional simulation and formal verification of digital designs, widely used for ASIC and FPGA verification.

Key Features

- UVM-based verification environment

- Formal verification and coverage analysis

- Assertion-based verification

- Regression management tools

- SystemVerilog and Verilog support

Pros

- Comprehensive functional verification

- Scalable regression testing

- Industry-standard methodologies

Cons

- User interface can be complex

- Requires specialized expertise

- Costly for smaller teams

Platforms / Deployment

- Linux, Windows

- Cloud / On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Integrates with Mentor and third-party simulation and synthesis tools.

- Testbench automation

- Waveform viewers

- Coverage and metric dashboards

Support & Community

- Dedicated support, webinars, and technical forums

4 — Siemens EDA (Calibre)

Short description: Calibre is an industry-standard tool for physical verification and design rule checking (DRC/LVS), ensuring manufacturability of IC designs.

Key Features

- DRC and LVS checks

- Layout vs schematic verification

- Extraction of parasitic elements

- Yield analysis and optimization

- Multi-process node support

Pros

- Reliable verification at scale

- Supports advanced process nodes

- Widely used in semiconductor fabs

Cons

- Requires dedicated training

- Processing time can be long for large designs

- Licensing costs are high

Platforms / Deployment

- Linux

- On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Integrates with multiple EDA design tools for full IC flow.

- API support for automation

- Compatible with third-party layout editors

- Data management and version control integration

Support & Community

- Enterprise support, strong technical documentation

#5 — Xilinx Vivado

Short description: Vivado is a design and verification toolset for FPGAs, offering synthesis, simulation, and timing analysis for programmable devices.

Key Features

- FPGA synthesis and implementation

- Hardware simulation and verification

- Timing and power analysis

- IP core integration

- RTL and high-level synthesis support

Pros

- Optimized for Xilinx FPGAs

- Strong simulation capabilities

- Easy integration of IP cores

Cons

- Limited to Xilinx devices

- Learning curve for beginners

- Resource-intensive

Platforms / Deployment

- Windows, Linux

- On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

- Integrates with Xilinx SDK and verification tools

- IP libraries

- Simulation and debug tools

- Scriptable APIs

Support & Community

- Technical support, active FPGA user community

6 — Synopsys VCS

Short description: VCS is a high-performance RTL simulator for functional verification, widely used in ASIC and FPGA development.

Key Features

- High-speed simulation

- SystemVerilog and Verilog support

- Coverage-driven verification

- Assertion-based verification

- Regression management

Pros

- Industry-leading simulation speed

- Comprehensive verification support

- Supports large designs

Cons

- Expensive

- Steep learning curve

- Limited analog capabilities

Platforms / Deployment

- Linux, Windows

- Cloud / On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

- Works with Synopsys Design Compiler and DFT tools

- APIs for automation

- Coverage reporting tools

Support & Community

- Enterprise-level support and user community

7 — Cadence Xcelium

Short description: Xcelium is a digital simulation platform offering mixed-signal verification and high-performance simulation for complex IC designs.

Key Features

- Parallel simulation architecture

- Mixed-signal support

- SystemVerilog and Verilog

- Assertion-based verification

- Coverage-driven testbench support

Pros

- High simulation performance

- Supports advanced verification methodologies

- Scales well for large designs

Cons

- Costly licensing

- Learning curve for complex flows

- Limited analog-only capabilities

Platforms / Deployment

- Linux, Windows

- Cloud / On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

- Integrates with Cadence toolchains

- Testbench automation APIs

- Reporting dashboards

Support & Community

- Enterprise support, documentation, and user forums

8 — Ansys RedHawk

Short description: RedHawk is a power, noise, and reliability analysis tool used for full-chip verification, focusing on advanced node designs.

Key Features

- IR drop analysis

- Electromigration checks

- Power integrity simulation

- Thermal analysis

- Multi-corner analysis

Pros

- Detailed power and noise analysis

- Scales for large ICs

- Integration with standard EDA flows

Cons

- Specialized expertise required

- Expensive for smaller teams

- Limited digital logic simulation

Platforms / Deployment

- Linux

- On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

- Integrates with physical verification and synthesis tools

- Supports automation APIs

- Compatible with other Ansys simulation suites

Support & Community

- Technical support, professional services

9 — Mentor Graphics ModelSim

Short description: ModelSim is a popular HDL simulation environment for ASIC and FPGA designs, providing functional simulation and debugging.

Key Features

- Verilog, VHDL, SystemVerilog simulation

- Waveform visualization

- Mixed-language support

- Debugging and breakpoints

- Testbench automation

Pros

- Easy to use

- Supports multiple HDLs

- Widely adopted in FPGA education and industry

Cons

- Slower for very large designs

- Limited advanced verification features

- Costly for enterprise versions

Platforms / Deployment

- Windows, Linux

- On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

- Works with other Mentor Graphics tools

- Scriptable testbenches

- IP core integration

Support & Community

- Enterprise support, active community, detailed tutorials

10 — Aldec Riviera-PRO

Short description: Riviera-PRO is a functional verification tool supporting mixed-language simulation and advanced verification methodologies for ASIC and FPGA designs.

Key Features

- Mixed-language support (VHDL, Verilog, SystemVerilog)

- UVM and OVM testbench support

- Assertion-based verification

- Coverage analysis

- Regression management

Pros

- Flexible and extensible

- Supports advanced verification methodologies

- Good FPGA support

Cons

- Limited analog simulation

- Enterprise licensing can be expensive

- Smaller user community

Platforms / Deployment

- Windows, Linux

- On-premises

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

- Integrates with popular synthesis and DFT tools

- API scripting support

- Waveform and reporting tools

Support & Community

- Technical support, documentation, and smaller but active community

Comparison Table (Top 10)

| Tool Name | Best For | Platform(s) Supported | Deployment | Standout Feature | Public Rating |

|---|---|---|---|---|---|

| Synopsys Design Compiler | Digital IC synthesis | Linux, Windows | Cloud / On-premises | AI-driven RTL optimization | N/A |

| Cadence Virtuoso | Analog/mixed-signal design | Linux, Windows | Cloud / On-premises | High-accuracy analog simulation | N/A |

| Mentor Graphics Questa | Functional verification | Linux, Windows | Cloud / On-premises | Formal & UVM verification | N/A |

| Siemens EDA Calibre | Physical verification | Linux | On-premises | Layout DRC/LVS | N/A |

| Xilinx Vivado | FPGA design | Windows, Linux | On-premises | FPGA IP integration | N/A |

| Synopsys VCS | RTL simulation | Linux, Windows | Cloud / On-premises | High-speed simulation | N/A |

| Cadence Xcelium | Mixed-signal simulation | Linux, Windows | Cloud / On-premises | Parallel simulation | N/A |

| Ansys RedHawk | Power/noise analysis | Linux | On-premises | Full-chip power/thermal verification | N/A |

| Mentor Graphics ModelSim | HDL simulation | Windows, Linux | On-premises | Waveform debugging | N/A |

| Aldec Riviera-PRO | Mixed-language verification | Windows, Linux | On-premises | Flexible testbench & coverage | N/A |

Evaluation & Scoring of IC Design & Verification Tools

| Tool Name | Core (25%) | Ease (15%) | Integrations (15%) | Security (10%) | Performance (10%) | Support (10%) | Value (15%) | Weighted Total (0–10) |

|---|---|---|---|---|---|---|---|---|

| Synopsys Design Compiler | 9 | 7 | 8 | 7 | 9 | 8 | 7 | 8.3 |

| Cadence Virtuoso | 9 | 6 | 8 | 7 | 8 | 8 | 6 | 7.8 |

| Mentor Graphics Questa | 8 | 7 | 8 | 7 | 8 | 7 | 7 | 7.6 |

| Siemens EDA Calibre | 8 | 6 | 7 | 7 | 8 | 7 | 6 | 7.2 |

| Xilinx Vivado | 8 | 7 | 7 | 7 | 8 | 7 | 7 | 7.5 |

| Synopsys VCS | 9 | 7 | 8 | 7 | 9 | 8 | 7 | 8.3 |

| Cadence Xcelium | 8 | 7 | 8 | 7 | 8 | 7 | 7 | 7.6 |

| Ansys RedHawk | 8 | 6 | 7 | 7 | 8 | 7 | 6 | 7.1 |

| Mentor Graphics ModelSim | 7 | 8 | 7 | 7 | 7 | 7 | 7 | 7.3 |

| Aldec Riviera-PRO | 8 | 7 | 7 | 7 | 7 | 7 | 7 | 7.3 |

Interpretation: Scores are comparative; tools with higher weighted totals generally offer broader capabilities, better integration, and performance for IC design and verification. Choice depends on workflow, design complexity, and device type.

Which IC Design & Verification Tool Is Right for You?

Solo / Freelancer

Focus on FPGA tools like Vivado or ModelSim for accessible workflows and cost-effectiveness.

SMB

Questa and Riviera-PRO offer flexible verification without full enterprise licensing costs.

Mid-Market

Synopsys Design Compiler and Cadence Virtuoso provide robust synthesis and simulation for growing IC teams.

Enterprise

Full-suite solutions like Synopsys VCS, Cadence Xcelium, and Calibre meet large-scale digital and analog verification needs.

Budget vs Premium

Start with FPGA/entry-level tools; scale to premium synthesis and verification suites for complex ICs.

Feature Depth vs Ease of Use

High-end tools offer maximum capability but require expertise; mid-tier options balance learning curve and functionality.

Integrations & Scalability

Select tools compatible with existing EDA flows to ensure smooth collaboration and scaling for large designs.

Security & Compliance Needs

Focus on tools offering IP protection, secure data handling, and compliance with internal enterprise security policies.

Frequently Asked Questions (FAQs)

1. What types of ICs can these tools support?

Most tools support digital, analog, mixed-signal, and FPGA IC designs depending on the specific tool’s focus and capabilities.

2. How steep is the learning curve for these tools?

Learning varies; enterprise tools like Virtuoso and VCS require significant training, while FPGA-focused tools like Vivado are easier for newcomers.

3. Can these tools run in the cloud?

Several tools support cloud deployment, enabling scalable simulations and collaborative workflows, though physical verification often remains on-premises.

4. Are there AI-driven features?

Yes, many tools offer AI-assisted optimization for synthesis, simulation speedup, and verification coverage enhancements.

5. What is the typical pricing model?

Enterprise licenses are often subscription-based or perpetual, with options for small team or academic pricing in some cases.

6. How do I integrate these tools with my existing workflow?

Most tools offer APIs, scripting capabilities, and integration with other EDA suites to fit into established design flows.

7. Are these tools suitable for FPGA design?

Yes, tools like Vivado and ModelSim are specifically optimized for FPGA development, while others focus on ASICs.

8. How is support structured?

Enterprise tools provide tiered support including documentation, training, and direct technical support; some have active community forums.

9. Can they handle large, complex ICs?

Yes, high-end tools like Design Compiler, Calibre, and VCS are designed to scale for large multi-million gate designs.

What are common mistakes in using IC design tools?

Common issues include insufficient verification coverage, misconfigured simulation environments, improper integration with EDA flows, and ignoring low-power constraints.

Conclusion

Selecting the right IC Design & Verification Tool depends on design complexity, IC type, team size, and budget. Enterprise teams benefit from comprehensive suites like Synopsys VCS or Cadence Virtuoso, while SMBs or FPGA-focused teams can use ModelSim or Vivado effectively. Prioritize tools that integrate with your workflow, offer strong verification coverage, and scale with project demands. A practical next step is to shortlist 2–3 tools, run pilot simulations, and validate integration and security before full adoption. Ensuring the right balance between capabilities, usability, and cost will optimize design outcomes and reduce time-to-market for your IC projects.

Find Trusted Cardiac Hospitals

Compare heart hospitals by city and services — all in one place.

Explore Hospitals